-

HDI PCB design guidelines

Designrichtlinien für HDI Leiterplatten

Designrichtlinien für hochdichte Leiterplatten

Hersteller von Leiterplatten (Printed Circuit Board, Leiterplatten) verwenden in der Regel drei Arten von Stapeln für Platten, die sie mit hochdichten Gehäusen bestücken:

-

Standardkaschierung mit Durchkontaktierungen oder durchkontaktierten Löchern

-

Sequentielle Kaschierung mit durchkontaktierten, verdeckten und vergrabenen Durchkontaktierungen

-

Kaschierung Aufbau mit Mikrovias

Von den drei oben genannten ist die letzte besonders geeignet für High Density Interconnect Leiterplatten (HDI Leiterplatten). Hemeixin Electronics Co., Ltd, ein bedeutender Hersteller von HDI-Leiterplatten, empfiehlt die Verwendung von Laminierung mit Microvias für HDI-Leiterplatten, die Ball Grid Arrays (BGA) und andere Fine-Pitch-Gehäuse mit hoher Pin-Anzahl haben, da jeder Typ seine eigenen Vor- und Nachteile hat.

So kann die Standardlaminierung mit Durchkontaktierungen bei 28 Lagen und darunter kostengünstig sein, ist aber sehr schwierig zu verlegen, wenn mehrere BGAs mit mehr als 1500 Pins und weniger als 0,8 mm Abstand beteiligt sind. Auch die sequentielle Laminierung mit Blind- und Buried-Vias hat potenziell kürzere Via-Stubs und relativ einfache Via-Modelle mit kleineren Via-Durchmessern als die für Through-Hole-Vias erforderlichen. Sequentiell laminierte Leiterplatten sind teurer als die Standardlaminierung mit Durchkontaktierungen, haben aber die gleichen minimalen Leiterbahnbreiten und ihre praktische Zuverlässigkeit beschränkt die Anzahl der Lagen auf maximal zwei oder drei.

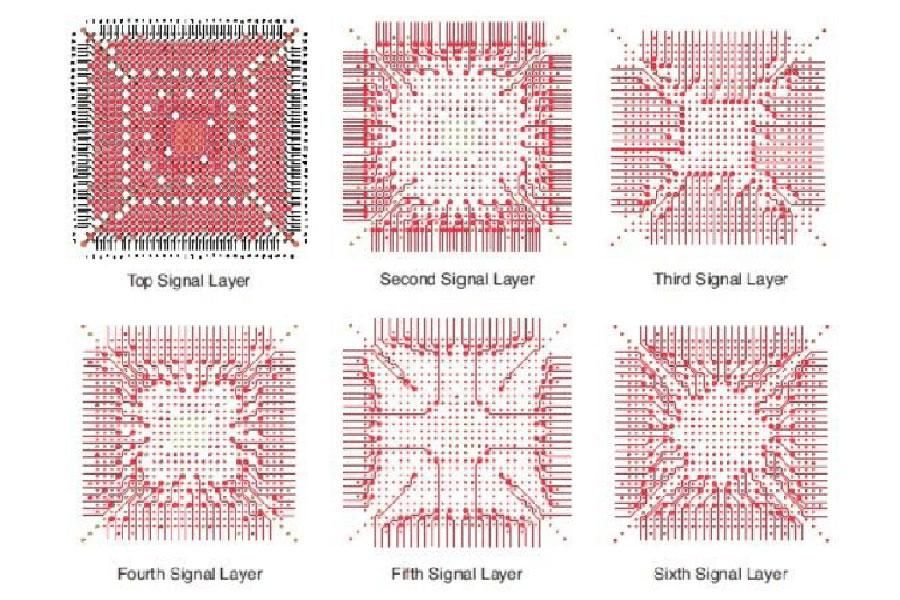

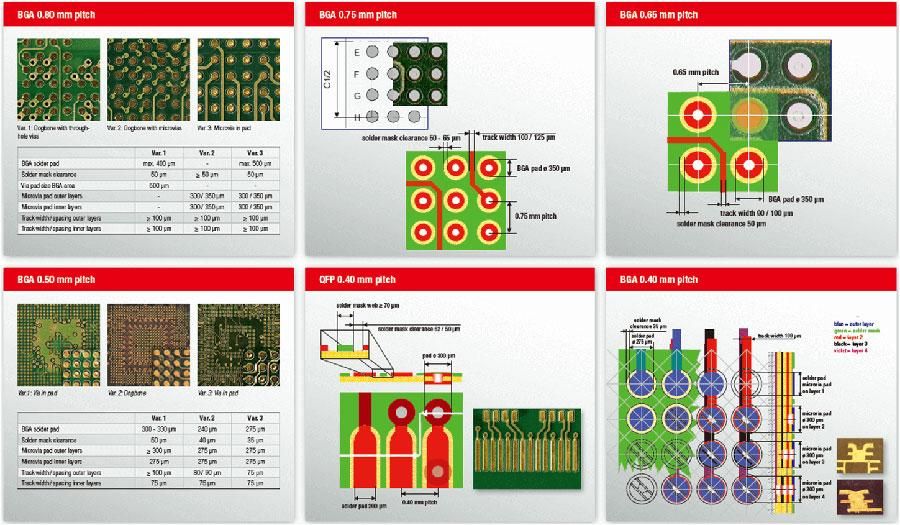

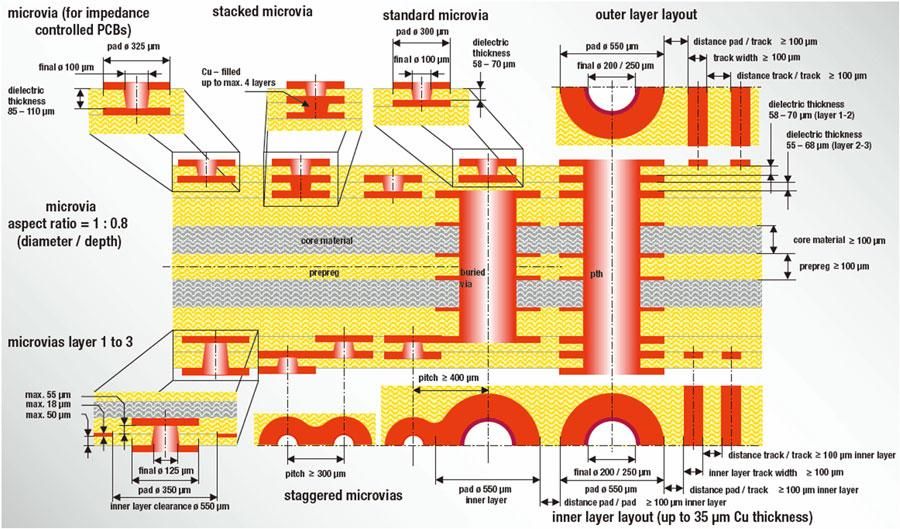

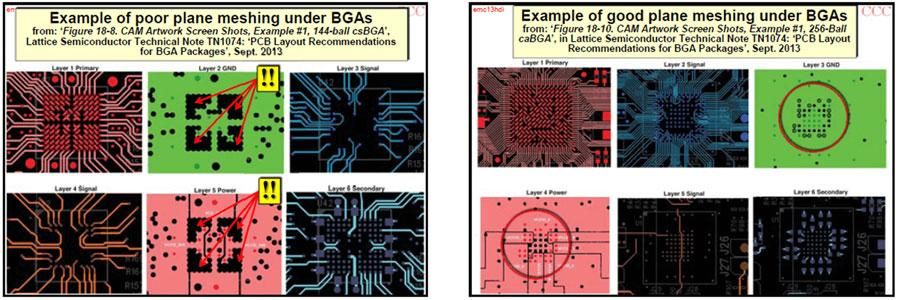

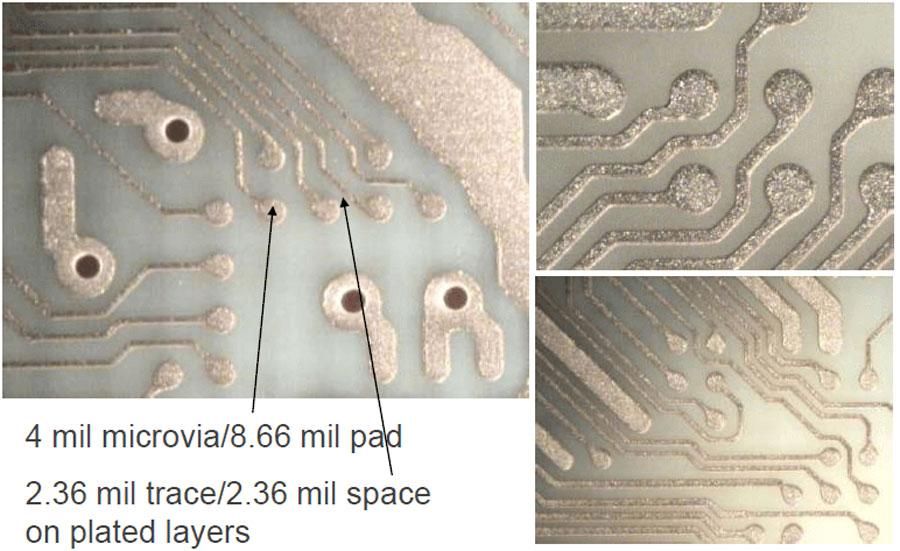

Diese und weitere Einschränkungen führen dazu, dass immer mehr Hersteller von HDI-Leiterplatten dazu übergehen, Laminate mit Microvias und anderen fortschrittlichen Merkmalen für HDI-Leiterplatten zu entwickeln. Zu den Vorteilen des HDI-Leiterplattendesigns mit Microvias gehört, dass mit weniger Lagen eine sehr hohe Leiterplattendichte erreicht wird, da die Leiterbahnen und Durchkontaktierungen vergleichsweise viel kleiner dimensioniert sind. Bei Microvia-HDI-Leiterplatten ergibt sich das Potenzial für eine geringere Anzahl von Lagen aus der effektiven Verwendung von Mustern mit Microvias, da dadurch mehr Platz für die Verlegung von Leiterbahnen zur Verfügung steht. Dies ist die einzige Möglichkeit, mehrere große BGAs mit feinem Raster und einem Abstand von 0,8 mm oder weniger zu entwerfen.

Die HDI-Technologie bietet die niedrigsten Kosten für Hochfrequenz-Leiterplatten mit hoher Dichte und verbessert bei geeigneter Stackup-Definition auch die Leistungs- und Signalintegrität in Hochfrequenz-Leiterplatten. Obwohl die typischen Materialien, die Hersteller für HDI-Leiterplatten verwenden, in Prozessen, die RoHS erfordern, gut funktionieren, bietet die Verwendung neuerer Materialien das Potenzial für höhere Leistung bei geringeren Kosten. Diese neueren Materialien sind jedoch nicht für die Herstellung von Leiterplatten mit Standard- oder sequentieller Laminierung geeignet.

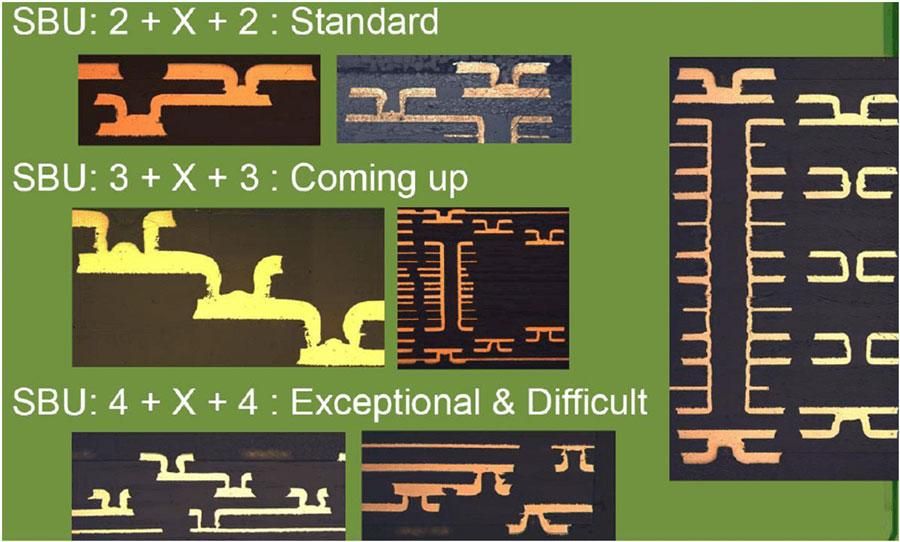

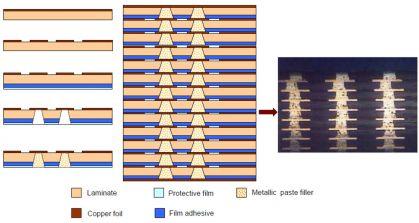

HDI ist eines der komplexeren Verfahren zur Herstellung von Leiterplatten, auf die wir uns spezialisiert haben. Wir verwenden die SBU-Technologie, die es ermöglicht, mehrere Lagenpaare nacheinander hinzuzufügen, um einen Multilayern Kern zu bilden, um diese Art von hochintegrierten Leiterplatten herzustellen.

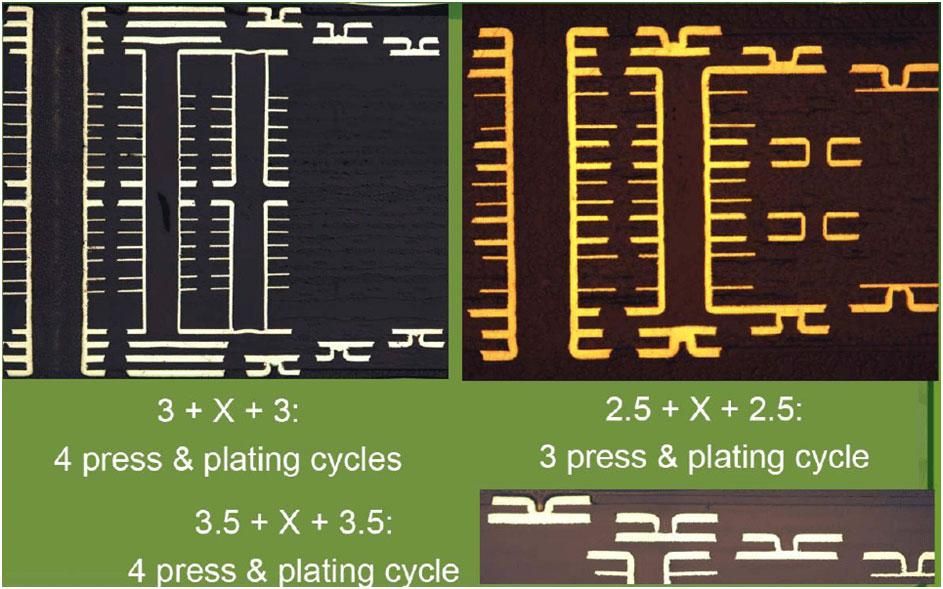

SBU ist eine Multilayer Technologie, bei der ein dielektrisches Element und eine Kupferfolie auf die Ober- und Unterseite des Kerns aufgebracht werden, bevor dieser einem Laserbohr-, Bildübertragungs- und Ätzverfahren unterzogen wird. Multilayer Leiterplatten, die mit diesem technologischen Verfahren hergestellt werden, sind durch eine Folge von Zahlen und N gekennzeichnet (z. B. 1+N+1, 2+N+2 usw.), wobei N für die Anzahl der Lagen steht, die den Kern bilden, und die Zahlenwerte für die Anzahl der hinzugefügten Lagen.

Moderne Leiterplattendesigner erhalten einen Überblick über robuste Regeln und Methoden, die es ihnen ermöglichen, eine äußerst zuverlässige Leiterplatte mit den niedrigsten Kosten, den am häufigsten verwendeten Merkmalen und der geringsten Anzahl von Fertigungsproblemen zu entwerfen (die dazu führen können, dass ein Angebot abgelehnt wird, technische Fragen auftauchen, der Auftrag auf Eis gelegt wird oder der endgültige Ertrag negativ beeinflusst wird).

High Density Interconnect (HDI)-Leiterplattendesigns haben eine höhere Verdrahtungs- und Pad-Dichte als herkömmliche Leiterplatten sowie geringere Leiterbahnbreiten und Abstände. Sie erfordern fortschrittliche Leiterplattentechnologien wie Blind Vias, Buried Vias und Microvias. HDI-Leiterplatten sind in der Regel teurer als herkömmliche Leiterplatten, da der Herstellungsprozess sehr komplex ist.

Wir möchten hier nur die Mindestanforderungen nennen, deren Einhaltung dem Designer eine äußerst zuverlässige Leiterplatte beschert.

Die folgenden Leitlinien enthalten diese Inhalte für Blind Vias, Buried Vias & Microvias Leiterplatten;

- Unterstützung bei der Fußabdruckgestaltung

- HDI Microvia Standard-Designregeln

- HDI Microvia Typen Definition

- Kosten der MicroVia HDI-Leiterplattentypen

- Plattiert durch hohes Aspektverhältnis

- Laminierzyklen bis zu 6 Mal für Stacked Microvia

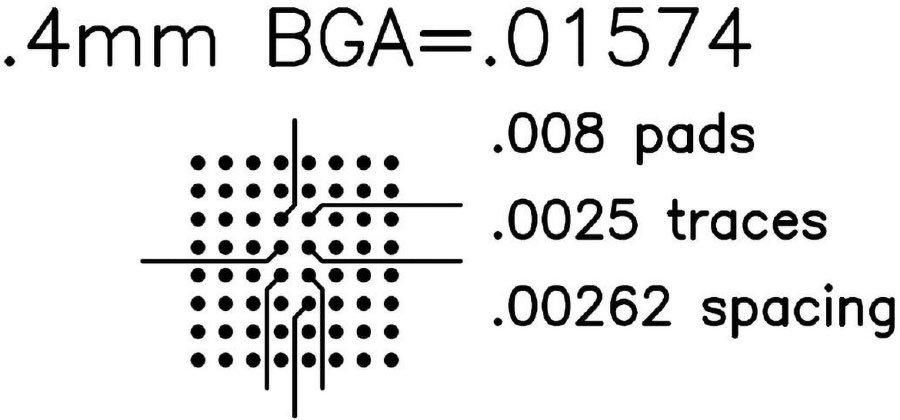

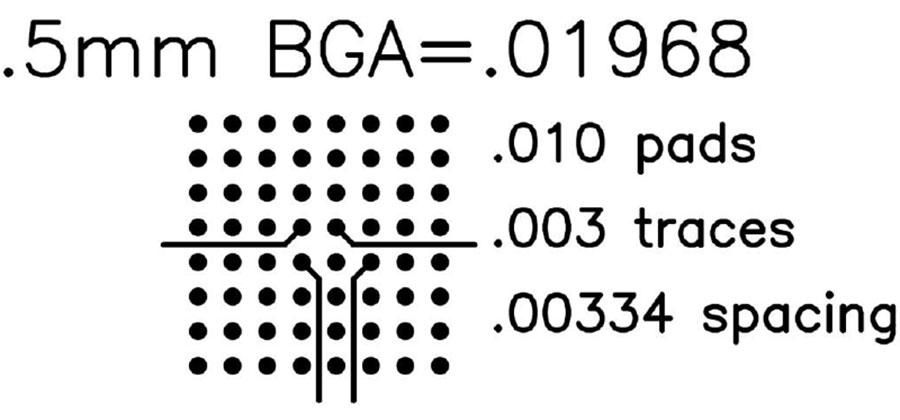

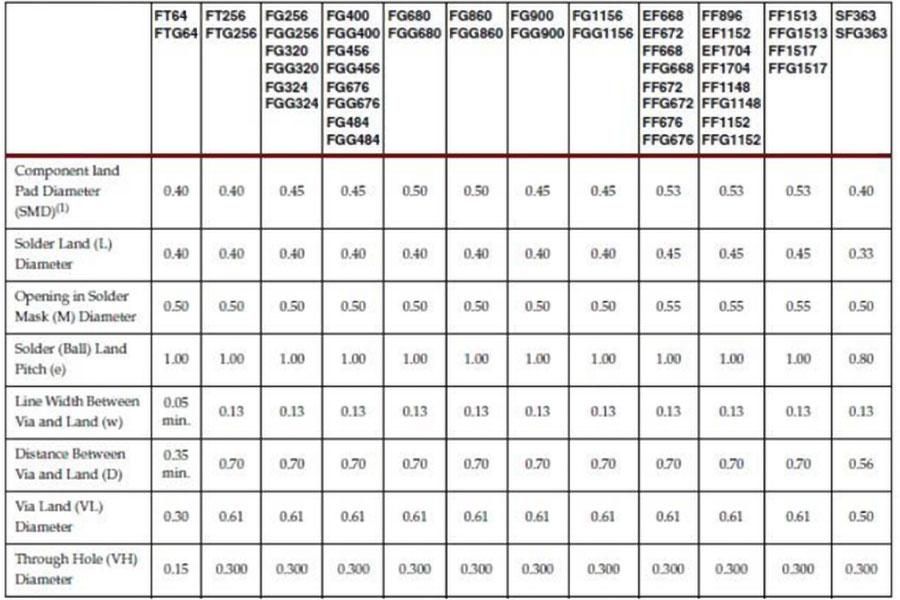

Unterstützung bei der Fußabdruckgestaltung

HDI Microvia Leiterplatten Standard Design Rules

Definition der HDI-Leiterplattentypen;

- 1 + n + 1 HDI-Leiterplatte 1 Schicht für Lasermikrovias, n Schichten für innere Schichten zwischen den Mikrovias.

- 2 + n + 2 HDI-Leiterplatte 2 Schichten für Lasermikrovias, n Schichten für Innenschichten zwischen den Mikrovias.

- 3 + n + 3 HDI-Leiterplatte 3 Schichten für Lasermikrovias, n Schichten für Innenschichten zwischen den Mikrovias.

- 4 + n + 4 HDI-Leiterplatte 4 Schichten für Lasermikrovias, n Schichten für Innenschichten zwischen den Mikrovias.

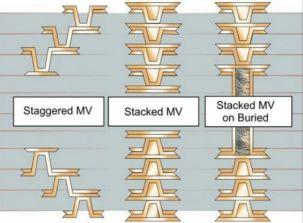

Stagger microvia 1+1+..+1+n+1+1+..+1 Every Layer Interconnect Leiterplatten

gestapelte Microvia hdi Platine

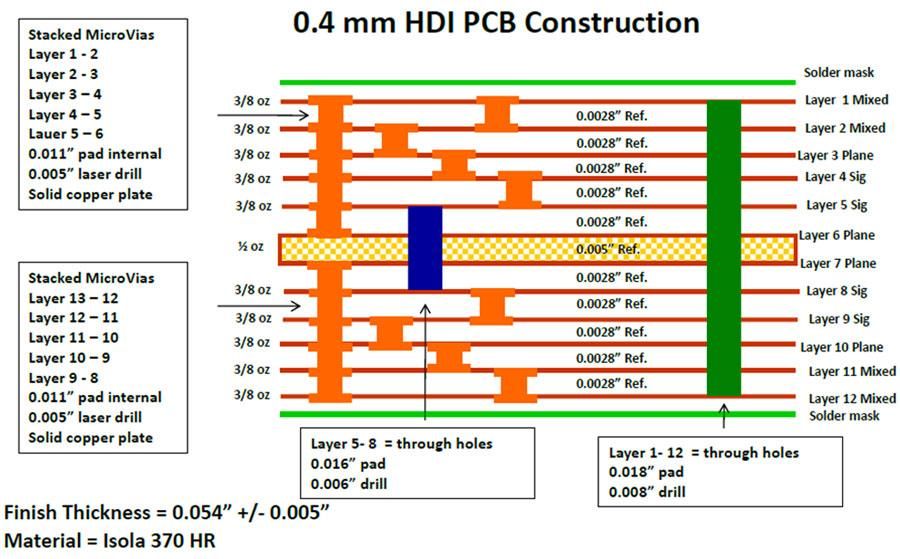

1+1+1+ ......+1+1+1 Stacked MicroVia 12 Lagen beliebige Lage HDI-Leiterplatte

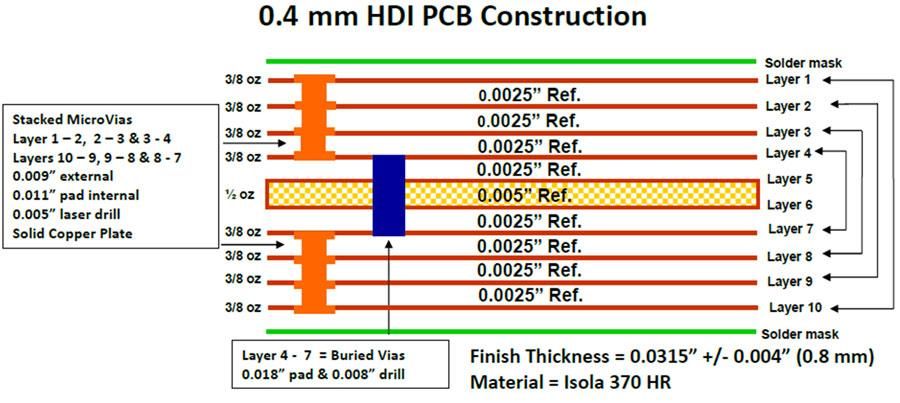

1+1+1+ n+1+1+1 Gestapelte MicroVia 10 Lagen Leiterplatte

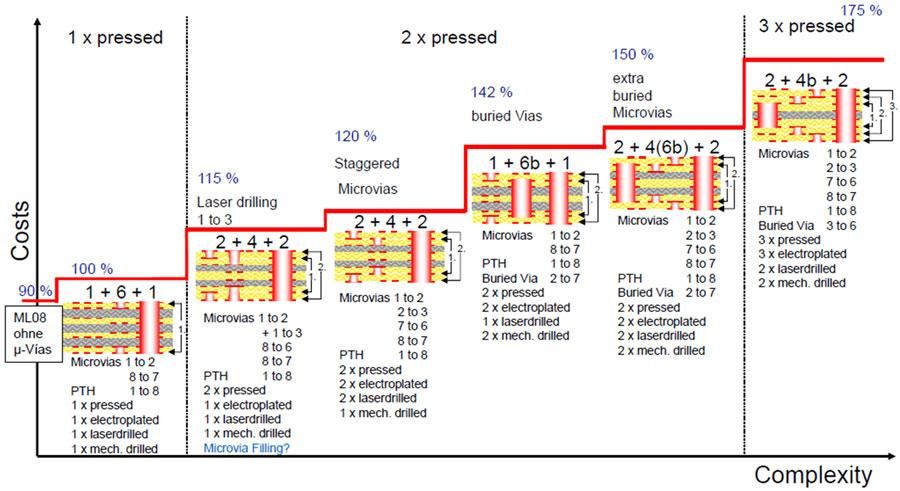

Kosten der MicroVia HDI-Leiterplattentypen

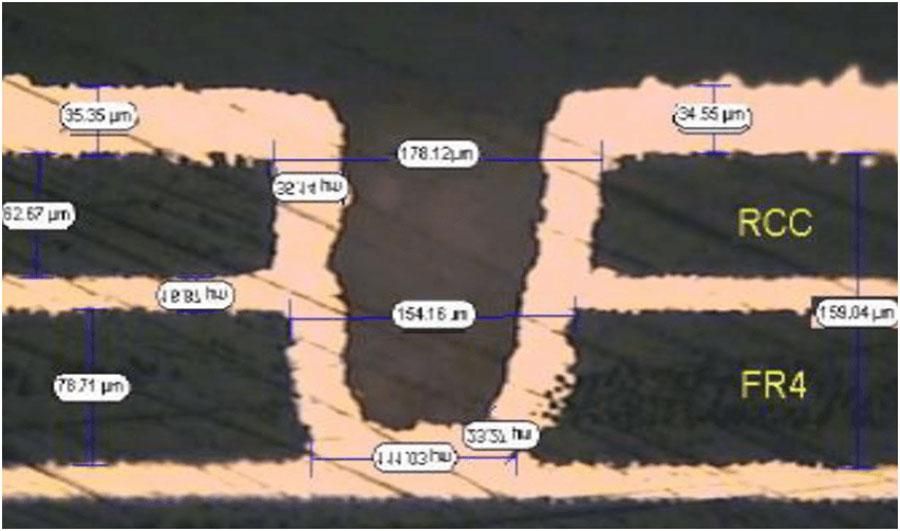

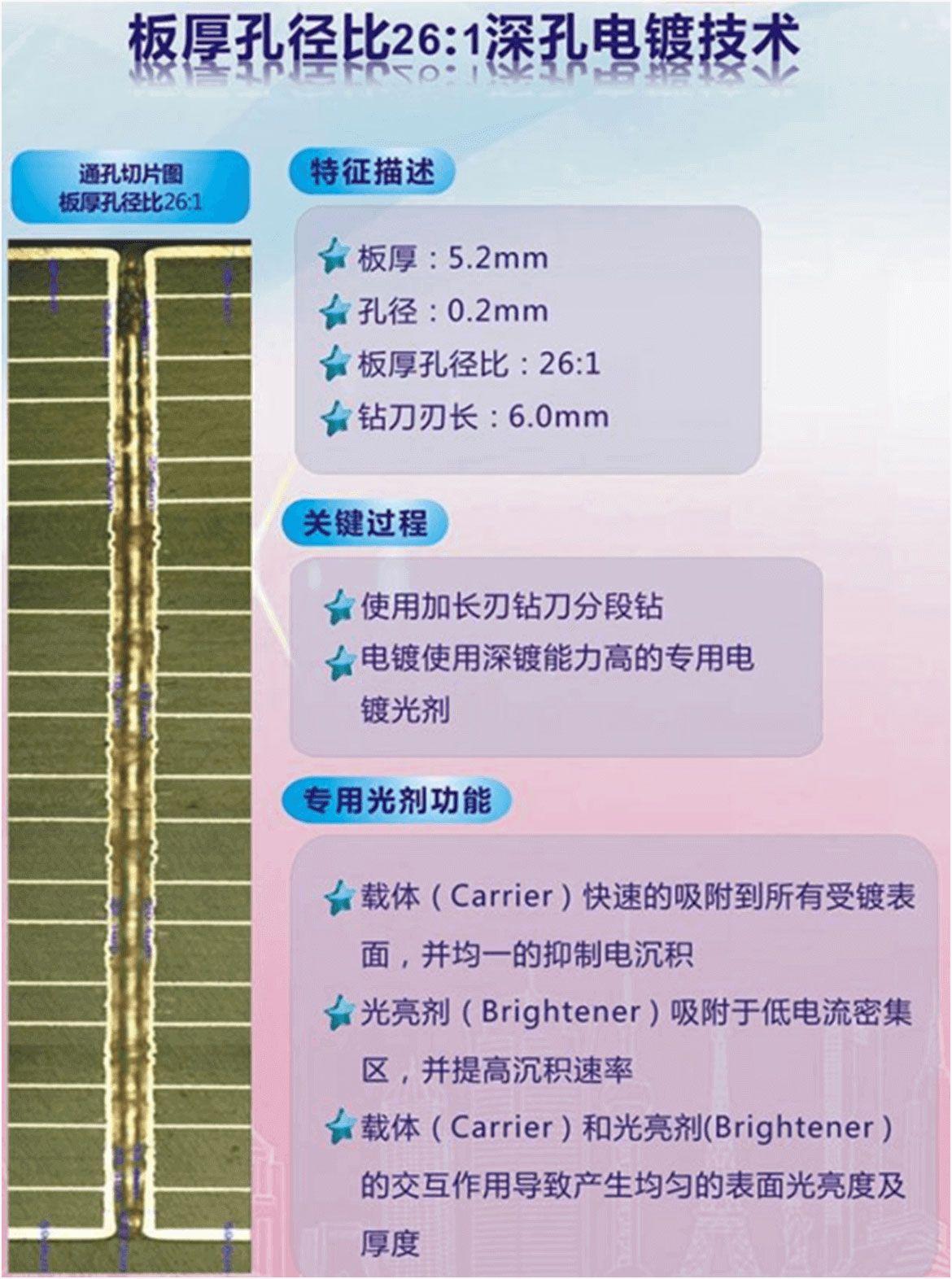

Plattiert durch hohes Aspektverhältnis

Bis zu mehrfache Laminierzyklen für Stacked Microvia Leiterplatten

Heute sind wir mit einer raschen Verkleinerung der Leiterplattengrößen konfrontiert, da der Formfaktor mit Fine-Pitch-BGAs und kleinen oberflächenmontierbaren Bauelementen verringert werden muss und alte Komponenten reduziert oder eliminiert werden müssen (ersetzt durch immer kleinere und dichtere Gehäuse).

Mit dem Aufkommen von Fine-Pitch-BGAs mit viel mehr Reihen von Verbindungen ist es notwendig, Microvias zu stapeln, um Oberflächensignale an mehrere darunter liegende Lagen zu leiten. Aufgrund der geringen Abstände ist eine einzelne Spur zwischen den Pads möglicherweise nicht möglich (wegen der stark verringerten Leitungsbreiten), so dass die Möglichkeit, eine weitere Schicht herunterzufahren, um das Signal aufzufächern, zwingend erforderlich ist.

Die Kehrseite davon ist die erhöhte WAK-Fehlanpassung zwischen der massiven Kupfer-Microvia-Struktur und dem umgebenden Laminat. Laminat-/Kupfer-Spannungsrisse sind bei Stapeln mit einer Höhe von mehr als 3 Metern (mit typischen LeiterplattenMicrovia-Durchmessern) wahrscheinlicher. Es sei darauf hingewiesen, dass in der CSP-Welt seit vielen Jahren erfolgreich Stapel mit einer Höhe von 5+ gebildet werden, allerdings mit viel kleineren Durchmessern und Dielektrika auf unterschiedlichen Substraten.

Hinzu kommt eine wachsende Zahl von Designern, die ohne Erfahrung in den erforderlichen Designtechnologien (Blind & Buried Vias, sequentielle Laminierung, Via-in-Pad, Laser-Microvias usw.) in den Beruf einsteigen. Anstatt spezifische Routing-Beispiele wie die folgenden zu geben, möchte ich mich lieber auf Design-Minimums konzentrieren, da diese Grenzen beim modernen LeiterplattenDesign routinemäßig verschoben oder überschritten werden.

In unserer hauseigenen Anlage in China haben wir bisher erfolgreich HDI-SBU mit einer Sequenzierung erstellt, die Any-Layer Interstitial Via Hole (ALIVH) in der HDI-Leiterplattenfertigung erreicht. Wir erreichen dies durch die Anwendung einer Metallisierungstechnik für die Verbindungslöcher (IVHs). Diese Methode bietet nicht nur eine stärkere Verbindung von gestapelten Durchkontaktierungen, sondern ermöglicht auch ein besseres Wärmemanagement, was die Zuverlässigkeit der Leiterplatte unter schwierigen Bedingungen deutlich erhöht.

Wir fertigen jedes Stück HDI-SBUs im eigenen Haus, dank unserer kompletten Palette an fortschrittlichen Maschinen und Anlagen. Zu den fortschrittlichen Geräten, die wir besitzen und betreiben, gehören Laser Direct Imaging-Maschinen, die zuverlässige und wiederholbare 2/2 mils mit dem begrenzten Lötmaskenabstand von 1 mil liefern können. Mit dieser fortschrittlichen Ausrüstung sind wir auch in der Lage, Probe Cards, DUTs und Load Boards für den Einsatz in der Halbleiterindustrie sowie Burn-In Boards mit bis zu 50 Lagen auf einer 0,276 Zoll dicken Platine mit einem Seitenverhältnis von 40:1, Metallkern- und Substrat-Leiterplatten mit 1,50 mils Leiterbahn und Abstand herzustellen.

Von der Konzeption bis zur Fertigstellung oder bei speziellen Problemen stehen unseren Kunden Konstrukteure zur Seite. Setzen Sie sich mit HemeixinLeiterplatten in Verbindung, um die Zusammenarbeit mit dem Konstrukteur zu beginnen, der Ihnen am besten bei Ihren spezifischen Konstruktionsanforderungen helfen kann. Bitte senden Sie Ihre E-Mail an Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!, wenn Sie Hilfe benötigen.

- Home

- Technologie

- Designrichtlinien für HDI Leiterplatten

- LeiterplattenTechnologie

- Leiterplatten Material

- Via-in-Pad

- Dickkupfer Leiterplatten

- Hochdichte Leiterplatten

- Impedanzkontrollierte Leiterplatten

- Hochfrequenz Leiterplatten

- Starrflex Leiterplatten

- Flexiblen Leiterplatten Biegen und Falten

- Aluminium Leiterplatte

- Designrichtlinien für Flex Leiterplatten

- Designrichtlinien für Starrflex Leiterplatten

- Designrichtlinien für HDI Leiterplatten

- Designrichtlinien für Dickkupfer Leiterplatten

- Fragen zum Flex LeiterplattenDesign

- Fragen zum Starrflex LeiterplattenDesign

- Fragen zum leiterplattenbestückung Design

-

Phone:

-

Email:Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!